# **MOCKOBCKN**N

авиационный инститчт

МЕТОДИЧЕСКИЕ УКАЗАНИЯ К КУРСОВОЙ РАБОТЕ по дисциплине «ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ и микропроцессорная **ТЕХНИКА»**

MO(KBA - 1991

COCYTAPCTBEHHHM KOMINTET CCCP TO HAPOJIHOMY OEPASOBAHMO

московский ориена ленина и ориена октябрьской революции АВИАЦИОННЫЙ ИНСТИТУТ имени СЕРГО ОРДЖОНИКИДЗЕ

**МЕТОЛИЧЕСКИЕ УКАЗАНИЯ** К КУРСОВОЙ РАБОТЕ ПО ДИСЦИПЛИНЕ "ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ И МИКРОПРОЦЕССОРНАЯ ТЕХНИКА"

> **Утверждено** на заседании редсовета I5 октября I990 г.

Москва Изпательство МАИ 1991

Московский авиационный институт, 1991

УДК: 681.325.5:621.382.049.77+681.322(075)

Авторы-составители: Б.С. Мельников, А.В. Щеглов

Методические указания к курсовой работе по дисциплине "Вычислительные системы и микропроцессорная техника" / Авт.-сост.: Б.С. Мельников, А.В. Щеглов. - М.: Изд-во МАИ, 1991. - 36 с.: ил.

Методические указания предназначены для студентов факультета радиоэлектроники летательных аппаратов, выполняющих курсовую работу по дисциплине "Вычислительные системы и микропроцессорная техника".

Определяются цели и задачи работы, направленные на закрепление у студентов знаний и навыков по построению цифровых устройств на современной элементной базе, порядок выполнения работы, требования к оформлению записки и порядок защиты.

Рассматривается пример построения цифрового устройства, на котором демонстрируется подход к выполнению курсовой работы.

МЕТОДИЧЕСКИЕ УКАЗАНИЯ К КУРСОВОЙ РАБОТЕ ПО ДИСЦИПЛИНЕ "ВЫЧИСЛИТЕЛЬНЫЕ СИСТЕМЫ И МИКРОПРОЦЕССОРНАЯ ТЕХНИКА"

Мельников Борис Сергеевич Пеглов Александр Васильевич

Редактор Г.Н. Борисова Техн. редактор В.Н. Горячева

Подписано в печать 05.06.91 Бум. офсетная. Формат 60х84 I/I6. Печать офсетная Усл. печ. л.2,09. Уч.-изд. л. 2,I2. Тираж 500 Зак. 243I / I76. Цена 20 к.

Типография издательства МАИ I2587I, Москва, Волоколамское шоссе, 4

# ТРЕБОВАНИЯ К ВЫПОЛНЕНИЮ И ОФОРМЛЕНИЮ КУРСОВОЙ РАБОТЫ

# І.І. ЦЕЛЬ И ЗАДАЧИ КУРСОВОЙ РАБОТЫ

Курсовая работа по дисциплине "Вычислительные системы и микропроцессорная техника" способствует развитию у студентов навыков проектирования цифровых устройств на современной элементной базе (БИС и микропроцессорах). Она помогает закрепить полученные ранее теоретические знания по оптимальному построению разрабатываемых устройств и микропроцессорных вычислителей и применению этих знаний для решения нестандартных задач, ранее не описанных в литературе.

Необходимо не только построить реальное работающее устройство, но и доказать, что это устройство, в некотором смысле, является наилучшим — наиболее просто решающим поставленную задачу, поэтому многовариантность решения является обязательным условием,

позволяющим постигнуть поставленной в работе цели.

#### 1.2. ЗАДАНИЕ НА КУРСОВУЮ РАБОТУ

Задание выдается в течение первой недели преподавателем-консультантом на вводной лекции, на которой каждый студент получает индивидуальное задание на курсовую работу. В задании указывается дата выдачи и защиты работы, приводятся исходные данные к разрабатываемому устройству.

Воякое цифровое устройство служит для преобразования входной информации в выходную, поэтому содержанием главной части задания является описание входной, выходной информации и требуемого закона преобразования. Возможны формы задания в виде: словесной формулировки, формулы преобразования, таблиц или графиков, эшор напряжений, схемы алгоритма и др.

Как правило, главная часть задания сопровождается вспомогательными требованиями к проектируемому устройству. К ним можно отнести:

быстродействие, время задержки на формирование выходных сигналов и тактовую частоту устройства;

- 2) способ синхронизации с источником и потребителем информации:

- 3) наличие внутренней индикации:

- 4) способы схемного самоконтроля расотоспособности устройства;

- 5) потребляемую мощность;

- 6) ограничения в выборе элементной бази;

- 7) наличие элементов ручного управления кнопок, тумблеров, переключателей;

- 8) характер питания (автономное, общее);

- 9) инициализацию устройства при включении питания и т.д.

Некоторые вспомогательные требования могут не указываться. В этом случае студент либо уточняет эти требования вместе с преподавателем, либо аргументированно выдвигает эти требования самостоятельно.

Основная группа тем, выдаваемых преподавателем, связана с разработкой специализированных устройств обработки информации с различными законами преобразования входных кодов в выходные. Например, темы могут быть сформулированы следующим образом:

- I. На вход устройства приходит код A $\{$  I:64 $\}$ . Определить в этом коде комбинации вида IIOII и установить номера разрядов, где расположены нули этих комбинаций.

- 2. Дан параллельный код A  $\{I:64\}$ . Разработать устройство, формирующее разность числа единиц и нулей кода, и выразить эту разность в прямом коде.

Этот список можно продолжить другими темами, в которых задаются различные законы преобразования кодов. Например, возможна разработка устройств для определения числа одинаковых кодов из ста приходящих на его вход параллельных кодов, кода с максимальным числовым эквивалентом среди множества двоичных позиционных кодов со знаком или без него и т.д. Все эти темы связаны с задачами специального вида обработки входной информации.

Наряду с ними могут выдаваться темы, связанные с разработкой отдельных узлов ЭВМ: арифметических устройств, множительных устройств с различными способами выполнения умножения, преобразователей десятичной информации в двоичную и обратно, интерфейсных устройств ввода-вывода информации и связи с внешними устройствами (преобразователями аналог-код, код-аналог, исполнительными устройствами и т.д.). Некоторые студенты самостоятельно изготавливают персональные компьютеры. В этом случае тема задания может отра-

жать интересы студента в этой области и содержать разработку узлов этого компьютера.

Тема задания может определяться также и тематикой научно-исследовательской работы студентов на кафедрах или СКБ, если она связана с построением цифровых вычислителей и по своему уровню не ниже стандартного задания на проектирование по дисциплине "Вычислительные системы и микропроцессорная техника".

#### 1.3. ПОРЯДОК ВЫПОЛНЕНИЯ КУРСОВОЙ РАБОТЫ

Работа с учетом многовариантности построения устройства включает в себя следующие этапы.

#### І.З.І. Уточнение задания

На этом этапе работи студент должен проанализировать задание, уточнить сведения о характеристиках и параметрах проектируемого устройства и определить дополнительную информацию, необходимую для реализации устройства в виде технического макета. Эта часть работы является наиболее ответственной, так как в правильной постановке задачи содержится 50% ее решения.

#### І.3.2. Выбор направления и обсуждение вариантов решения задачи

Прежде всего необходимо решить, к какому классу относится разрабатываемое устройство — к классу комбинационных или к классу регистровых (автоматных) устройств. Если оно может быть построено как в комбинационном, так и регистровом исполнении, то выбор метода реализации должен быть предельно полно обоснован. Допустима и двойная реализация устройства с последующим сравнительным анализом вариантов в курсовой работе.

При регистровом методе реализации цифрового устройства необходимо обосновать выбор одного оптимального варианта из нескольких возможных вариантов. Сравнение вариантов и выбор простейшего

решения может производиться на различных этапах: составления схемы алгоритма, операционного описания устройства, разработки функциональной, а также принципиальной схемы устройства. Возможна реализация нескольких вариантов с последующим сравнительным анализом

в конце курсовой работы.

Рекомендуется в качестве одного из направлений регистровой реализации использовать стандартную структуру микропроцессорного

вычислителя на КР58ОВМ80, для которой в обязательном порядке составляется программа на языке ассемблера [17, 18]. Могут быть использованы микропроцессоры КІ8ІОВМ86, КІ8ІОВМ88, КРІ82ІВМ85 [19, 22] и др. Программа отлаживается на персональных ЭВМ, микроЭВМ или на лабораторной микроЭВМ "Микролаб". В последнем случае ассемблерная программа вручную транслируется в программу на машинном языке в системе команд микропроцессора КР58ОВМ80.

Обсуждение вариантов решения ведется в словесной форме, общей для различных методов технического решения задачи. При необходимости могут привлекаться методы задания комбинационных схем, алгоритмические и языковые средства описания функционирования операционных устройств.

#### І.З.З. Составление схемы алгоритма

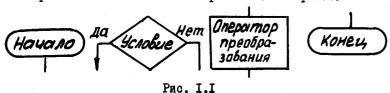

Первоначальное формализованное описание функционирования устройства выполняется с помощью схемы алгоритма. Она включает в себя совожупность операторов преобразования и операторов перехода (рис. I.I). Схема начинается с оператора "Начало", который может обозначать включение устройства, инициализацию начального состояния, начало обработки входных сигналов и т.д., и завершается оператором "Конец", который может обозначать окончание обработки очередного кода, переход в режим ожидания, выключение устройства и т.д. Рекомендуется использовать операторы переходов на два направления, котя применение переключателей на большее число переходов также допустимо. На степень детализации алгоритма никаких ограничений не накладывается, необходимо следить лишь за тем, чтобы разветвления и циклы проявляли себя в схеме алгоритма явным образом.

Желательно, чтобы в операторах преобразования и переходов имена шин и операционных элементов использовались явно. Условия переходов должны записываться содержательно в виде логических или арифметических выражений, а не в виде переменной, обозначаемой  $P\dot{z}$ . Использование идентификаторов допустимо, если они являются именами разрядов устройств или шин. При составлении охемы алгоритма целе-

сообразно отделять действия, выполняемые человеком-оператором, от действий, выполняемых устройством управления, так как только по-следние требуют технической реализации.

Если разрабатывается несколько алгоритмов, то их представление должно быть предельно идентичным, поскольку только в этом случае можно качественно и количественно сравнивать предлагаемые решения.

#### І.3.4. Составление операционного описания

Операционное описание синтезируемого устройства составляется на учебном языке операционного описания (УЯОО). Возможно использование языков описания цифровых устройств и языков регистровых передач, применяемых для моделирования сложных цифровых устройств таких, как языки СДС, ДДС [7, 10].

Операционное описание является выражением алгоритма в терминах действий, выполняемых операционными элементами, — микроопераций. Поэтому при описании внутренних переменних надо учитывать и меющуюся в распоряжении разработчика элементную базу. Для упрощения операционного описания допускается вводить в него нестандартные элементы, например трехвходовые сумматоры или регистры, осуществляющие сдвиг на 72 разрядов. Такие элементы должны быть описаны в виде программных модулей операционного описания.

При составлении операционного описания могут быть выявлены неточности в решающем алгоритме, которые потребуют либо изменения последовательности микрокоманд, либо включения новых микрокоманд. В этом случае исходний алгоритм обязательно исправляется. Таким образом, должно строго соблюдаться однозначное соответствие схемы алгоритма и операционного описания. Если замечено хоть малейшее отклонение одного от другого, то соответствие должно быть восстановлено изменением либо схемы алгоритма, либо операционного описания.

При переходе от схемы алгоритма к операционному описанию необходимо учитывать параллельность протекающих в устройстве процессов. Это обстоятельство заставляет особенно внимательно подходить к последовательной записи одновременно реализуемых операторов.

Для упрощения управляющего автомата выделяют совместние, условно-эквивалентные и эквивалентные по управлению микрокоманды. Операционное описание переписывают в терминах эквивалентных управляющих сигналов, учитывая, что условно-эквивалентные сигналы формируются непосредственно в операционном автомате.

# І.3.5. Построение функциональной схемы операционного автомата

Функциональная схема операционного автомата (ОА) должна включать набор операционных элементов, связи между ними, связи этих элементов с входными и выходными шинами устройства, связи с управляющим автоматом (УА).

#### 1.3.6. Построение функциональной схемы управляющего автомата

На этом этапе работы рекомендуется строить УА в двух вариантах - с жесткой и программируемой логикой.

При построении УА с жесткой логикой можно использовать как идеи класоического синтеза конечных автоматов [13, 14], так и идеи реализации УА на счетчиках, распределителях импульсов и дешифраторах [16]. Выбор метода построения определяется вкусами разработчика.

Для построения управляющего автомата с жесткой логикой в виде конечного автомата следует получить граф переходов и выходов. Для этого необходимо построить граф-схему алгоритма. На схеме в операторах преобразования указываются только управляющие сигналы без перечисления выполняемых под их воздействием микроопераций; в операторах перехода указываются только переменные условия перехода, а направления переходов отмечаются значением этой переменной — О или І. Переход от граф-схемы алгоритма к графу переходов и выходов автомата осуществляется в соответствии с методикой, изложенной в [15]. Он составляется как для автомата Мура, так и автомата Мили, после чего выбирается лучший автомат с меньшим числом состояний.

Выбор метода адресации для УА с программируемой логикой определяется характером решающего алгоритма — отношением числа операционных микрокоманд к числу управляющих микрокоманд. Как правило, лучшие результаты дает применение "естественной" адресации. Тогда работа по созданию УА будет заключаться в построении стандартной структуры УА, выборе элементов и написании соответствующей микропрограммы. На этом этапе работ целесообразно рассмотреть и обсудить несколько вариантов форматов микрокоманд и выбрать оптимальный.

# І.4. ОФОРМЛЕНИЕ КУРСОВОЙ РАБОТЫ

Куроовая работа оформляется в виде расчетно-пояснительной записки, включающей рукописный текст и графику общим объемом 25 - 30 страниц формата A4. Записка должна включать следующие основные разделы, расположенные в порядке выполнения расоты:

- I) оглавление;

- 2) задание на проектирование;

- 3) выбор направления решения;

- 4) схему алгоритма функционирования устройства;

- 5) операционное описание устройства;

- 6) функциональную схему операционного автомата;

- 7) функциональную схему управляющего автомата;

- 8) принципиальную схему устройства;

- 9) построение устройства в виде микропроцессорного вычисли-

- IO) заключение;

- II) список использованной литературы.

Схемы алгоритмов и принципиальные схемы должны выполняться в соответствии с требованиями ГОСТ и ЕСКД [36, 37]. Все рисунки нумеруются и помещаются в записке после первых ссылок на эти рисунки. Если рисунок выполнен на отдельном листе, то он помещается за страницей текста, содержащей ссылку.

В записке не допускаетоя сокращение слов, кроме общепринятых (ЭВМ, МП, ОЗУ, ПЗУ и др.). Все нестандартные аббревиатуры должны быть обязательно расшифрованы. Формулы, приводимые в записке, могут иметь номера, на которые можно ссылаться в тексте. Номера размещаются с правой стороны у кромки листа в круглых скобках.

Записка вкладывается в обложку из ватмана и орошоруется. Лицевая сторона обложки является титульным листом и оформляется так, как показано на рис. I.2. При сквозной нумерации страниц в записке этот лист считается первой страницей. Титульный лист подписывается студентом и преподавателем.

При оформлении работы в записке должен найти отражение не только наилучший вариант, но и материал, демонстрирующий весь путь движения к цели. Оформление записки производится по частям в порядке завершения работы над отдельными ее разделами.

#### І.5. КАЛЕНЦІАРНЫЙ ПЛАН ВЫПОЛНЕНИЯ КУРСОВОЙ РАБОТЫ

Руководство курсовой работой и ее организацию осуществляет кафедра. Календарный план является графиком работы студентов и кафедра строго следит за его выполнением. Каждый студент обязан один раз в неделю отчитываться перед преподавателем о проделанной рабо—

# МОСКОВСКИЙ ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ АВИАЦИОННЫЙ ИНСТИТУТ имени СЕРГО ОРДЖОНИКИДЗЕ

Кафедра 4 0 3

РАСЧЕТНО-ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

к курсовой работе по дисциплине "Вычислительные системы и микропроцессорная техника"

Выполнял

отудент группы

подпись, дата

Консультировал

подпись, дата

Фамилия И.О.

Москва 199 те. Преподаватель еженедельно определяет процент выполнения студентом курсовой работы. Эти данные вывешиваются на специальном стенде кафедры.

Примерный календарный план выполнения работы рассчитан на 17 недель и приведен в табл. I:

Таблица І

| <b>№</b><br>п/п | Наименование этапа работы               | Неделя     | Объем, % |

|-----------------|-----------------------------------------|------------|----------|

| I               | Изучение задания                        | I          | I        |

| 2               | Разработка схемы алгоритма              | - 3        | 20       |

| 3               | Составление операционного описания      | 4          | 25       |

| 4               | Построение функциональной схемы         |            |          |

| i               | устройства                              | 6          | 35       |

| 5               | Построение принципиальной схемы         |            |          |

| 1               | устройства                              | 10         | 50       |

| 6               | Разработка программы для МІ вычислителя | 12         | 60       |

| 7               | Оформление записки                      | <b>I</b> 5 | 90       |

| 8               | Защита куроовой работы                  | 17         | 100      |

Защита курсовой работы происходит перед комиссией, в которую соязательно входит и преподаватель-консультант. Защита может осуществляться в присутствии всей учебной группы.

# 2. ПРИМЕР ПОСТРОЕНИЯ ЦИФРОВОГО УСТРОЙСТВА

На примере решения демонстрационной задачи покажем весь путь выполнения курсовой работы от постановки задачи до получения принципиальной схемы реального устройства.

#### 2.1. ЗАДАНИЕ НА ПРОЕКТИРОВАНИЕ

Первоначальная формулировка задания выглядит следующим образом:

на вход устройства приходит 32-разрядный параллельный код A  $\{1:32\}$ ; на выходе устройства сформировать код B $\{1:\kappa\}$ , отображающий число единиц кода A.

Такая формулировка является явно недостаточной. Действительно, задание на преобразование кода A в код В требует дополнительной информации:

- I. Каков период / поступления входных кодов, сколько времени отводится на преобразование? Техническое решение естественно будет разным в случае разделения входных кодов интервалами в 100 нс, I мко и 10 мкс. Коды могут поступать асинхронно после преобразования предыдущего кода в устройстве. Если значение / не задается, то можно расомотреть несколько вариантов построения устройства, оценить их быстродействие и определить область их применения.

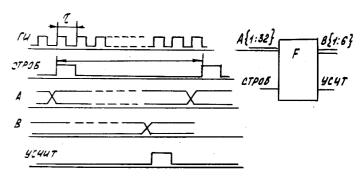

- 2. Каким образом синхронизируется работа устройства с источником и потребителем информации? Примем, что источник входного кода гарантирует правильность выставленной информации во время действия отробирующего импульса СТРОБ, а само устройство подтверждает выдачу кода числа единичных символов генерацией импульса считывания усчит.

Здесь же решается вопрос о виборе тактовой синхронизирующей последовательности импульсов: или она будет общей для источника, устройства преобразования и потребителя информации (внешняя синхронизация), или она будет формироваться с помощью автономного генератора тактовых импульсов (ГТИ), установленного в разрабатываемом устройстве (внутренняя синхронизация). Выберем внешнюю синхронизацию с частотой ГТИ - 5 МГц.

При внешней синхронизации необходимо уточнить привязку входных и выходных сигналов по отношению к тактовой последовательности импульсов. Будем считать, что смена кодов A и В осуществляется по положительному фронту импульсов ГТИ, длительность импульсов СТРОБ и УСЧИТ равна периоду тактовой последовательности и положительные фронты этих импульсов появляются вслед за положительным фронтом импульсов ГТИ.

3. Каково отображение кода A в код В? Для решения задачи необходимо установить однозначное соответствие между кодом В и кодом A. Это соответствие определяется многими факторами: удобством оценки, необходимостью передачи на уровне помех, требованиями использования кодов для обнаружения и исправления ошибок, удобством индикации и многими другими факторами.

Примем, что выходной код В  $\{I: \kappa\}$  — двоичный позиционный код, численный эквивалент которого равен числу единичных символов кода А  $\{I: 32\}$ . Легко заметить, что максимальное число "единиц", равное 32, потребует формирования шестиразрядного выходного кода В  $\{I: 6\}$ , так как  $(32)_{TO} = (100000)_2$  (32Д = 100000B).

В качестве сопутствующей можно рассмотреть задачу формирования выходного кода в двоично-десятичном представлении. Разрядность при

этом не изменится: потребуется тетрада для формирования младшей цифры (0-9) и два двоичных разряда для представления старшей цифры (0-3). Представляет интерес введение контрольного разряда В  $\{7\}$  для проверки кода на четность (нечетность) при передаче по каналу связи.

Итак, задание на проектирование может быть выражено в виде функциональной схемы и эпюр напряжения, изображенных на рис. 2.1.

PMC. 2.I

Примем, что в разрабатываемом устройстве не требуется введения внутренней индикации, и не будем пока накладывать никаких ограничений на потребляемую устройством мощность и, следовательно, на выбор оптимальной элементной базы. Эти вопросы могут быть решены при дальнейшей работе над заданием.

Разработка схемы устройства начинается с главного вопроса - определения метода построения устройства как комбинационного или как регистрового. Согласно заданию устройство преобразует входной параллельный код в выходной, поэтому оно может быть построено и как комбинационное, и как регистровое. Рассмотрим оба варианта, сравним сложность их реализации и определим область применения.

#### 2.2. КОМБИНАЦИОННАЯ РЕАЛИЗАЦИЯ УСТРОЙСТВА

При построении устройства в виде комбинационной схемы надо решить задачу синтеза системы шести логических функций 32 переменних. Эта задача достаточно сложна и в условиях ограниченного времени проектирования решена быть не может.

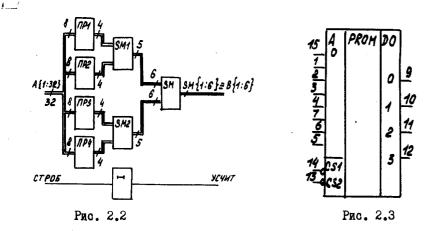

К решению задачи можно подойти с позиций операционного синтеза, построив устройство, реализующее цепочку простых преобразований. Разобыем входной код на такие части, для которых решение задачи преобразования "числа единиц" в позиционный двоичный код является практически реализуемым. Разобьем входной код на четыре части: A  $\{1:32\}$  = A  $\{1:8\}$ . A  $\{9:16\}$ . A  $\{17:24\}$ . A  $\{25:32\}$ .

Каждый байт преобразуется в число единиц с помощью цифрового устройства, которое назовем преобразователем кода и будем обозначать через  $\pi$  {I:4} (i = 1,2,3,4). Тогда

$$B\{1:6\} = \Pi P1\{1:4\} + \Pi P2\{1:4\} + \Pi P3\{1:4\} + \Pi P4\{1:4\}.$$

Будем формировать сумму в два этапа - суммированием кодов пары преобразователей и суммированием полученных сумм:

Здесь PI и P2 - сигналы переноса 4-разрядных сумматоров SM1 и SM2.

Функциональная схема устройства изображена на рис. 2.2. Сигнал УСЧИТ образуется путем задержки сигнала СТРОБ на максимально возможное время формирования выходного кода. Оно зависит от выбранной элементной базы.

Для построения сумматоров SM1 и SM2 воспользуемся микросхемой КІ55ИМЗ (4-разрядный сумматор), а для построения сумматора SM - макросхемами КІ55ИМЗ, КІ55ИМЗ (КІ55ИМЗ - 2-разрядный сумматор). Задержка в формировании выходного сигнала этими сумматорами составляет не более 40 нс.

Преобразователи кодов *ПРІ* являются нестандартными устройствами. Анализ показывает, что использование логических элементов (элементов с "жесткой" структурой) приводит к очень объемной реализации. Возникает мысль об использовании программируемых структур — электрически программируемых постоянных запоминациих устройств (IIIЗУ) или программируемых логических матриц. Первая структура более доступна; поэтому будем использовать микросхему КР556РТ4, изображенную на рис. 2.3. Эта микросхема совместима с ТТЛ-элементами (ТТЛ — транзисторно-транзисторная логика) и обеспечивает задержку не более 70 нс. Программирование этого IIIЗУ будем проводить по таблице истинности функции преобразования 8-разрядного кода в 4-разрядный (табл. 2).

Таблина 2

| AO | AI | .A2 | АЗ | A4  | <b>A</b> 5 | <b>A</b> 6 | .A7 | DО | DI | <b>D</b> 2. | Д3 |

|----|----|-----|----|-----|------------|------------|-----|----|----|-------------|----|

| 0  | 0  | 0   | 0  | 0   | 0          | 0          | 0.  | 0  | 0  | 0           | 0  |

| I  | 0  | 0   | 0  | 0   | 0          | 0          | 0   | I  | 0  | 0           | O  |

| 0  | I  | 0   | Ö  | 0   | 0          | 0          | 0   | I  | 0  | 0           | 0  |

| I  | I  | 0   | 0  | 0   | 0          | 0          | 0   | 0  | I  | 0           | 0  |

| -  | -  | -   | -  | l – | -          | -          | _   | -  | _  | _           | _  |

| I  | I  | . I | I  | I   | I          | ·I         | I   | 0  | 0  | 0           | I  |

Проектируемое устройство строится на восьми корпусах микросхем. Оно может использоваться в системах, в которых допустимое время формирования выходного кода не превышает 150 нс: действительно, задержка выходного кода

$$T = T(\Pi\Pi 3Y) + T(SM1,SM2) + T(SM) = T(KP556PT4) + T(K155UM3) + T(K155UM3 + K155UM2) = TO + 40 + 40 = 150 HC.$$

Преобразователь на стандартных логических элементах может быть построен из двух 4-битовых преобразователей и 3-разрядного сумматора. Если XO, XI, X2, X3 - биты 4-разрядного поля входного слова, Y0, YI, Y2 - биты выходного слова 4-битового преобразователя, определяющего двоичный позиционный код числа единиц поля входного слова, то, рассматривая Y0, YI, Y2 как логические функции переменных X0, XI, X2, X3, получим следующие логические выражения выходов преобразователя для реализации на элементах И-НЕ и ИСКЛО-ЧАЮЩЕЕ ИЛИ (mod 2):

Y0=A0 mod 2 A1 mod 2 A2 mod A3, Y1=(A0/A2/A3)/(A0/A1/A2)/(A0/A2/A3)/(A0/A1/A3), Y2=A0/A1/A2/A3.

Преобразователь на восемь разрядов, построенный из двух 4-битовых преобразователей на элементах КІ55ЛНІ, КІ55ЛІБ, КІ55ЛА4, КІ55ЛА2, КІ55ЛАІ, КІ55ИМЗ, содержит двенадцать корпусов вместо одного корпуса ШЗУ.

#### 2.3. РЕГИСТРОВАЯ РЕАЛИЗАЦИЯ УСТРОЙСТВА

Комбинационная реализация разрабатываемого устройства имеет крупний недостаток - объем устройства растет пропорционально длине входного кода. Поэтому целесообразно комбинационную реализацию применять при длине кода не более 32 бит. В ряде практических случаев приходится подочитывать число единиц в многоразрядных оловах, длина которых заранее не определена. Оторда следует. что преобразователь "чиола единиц" в двоичный позиционный код должен быть более гибким, более универсальным.

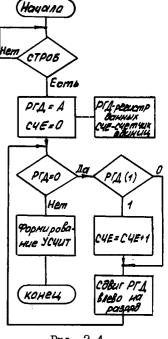

В основу построения регистрового варианта устройства положим идею преобразования параллельного кода в последовательный с последующим счетом числа единичных символов. Такое преобразование полжно начинаться с момента прихода входного кода и сигнала СТРОБ и заканчиваться моментом окончания счета единичных символов с генерацией импульса считывания. Таким образом, задача преобразования распадается на две подзадачи: преобразование параллельного кода в последовательный и получение выходного кода с формированием УСЧИТ.

Первая подзадача решается двумя путями: первый состоит в использовании мультиплексора, второй - сдвигового регистра. Первый вариант требует фиксации входного кода на все время преобразования. Второй вариант является более универсальным. Для его реализации достаточно выставить входной код А { 1:32} на время сигнала СТРОБ. В учесном пособии рассмотрим только второй вариант, котя первый вариант также представляет интерес и может онть проработан в курсовой работе как альтернативный вариант.

Вторую подзадачу - формирование выходного кода - можно решить либо путем создания детерминированной последовательности управляющих сигналов одвига всех разрядов кода через выходной разряд регистра, либо формированием признака очищения регистра от единичных символов в процессе сдвига. Первый вариант потребует установки дополнительного счетчика циклов, второй вариант - введения схемы анализа содержимого регистра на нулевое значение. При несколько больших затратах второй вариант обеспечивает в среднем более быстрое преобразование, поокольку последние нули кода преобразованию не подвергаются. Примем второй вариант определения конца преобразова-16

ния в качестве рабочего, тогда, естественно, применение сдвигового регистра становится обязательным.

# 2.3.1. Разработка схемы алгоритма и составление операционного описания

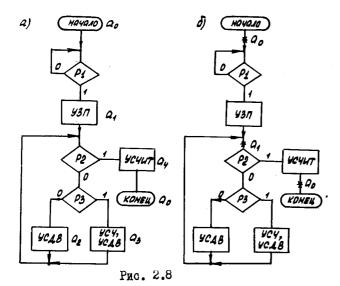

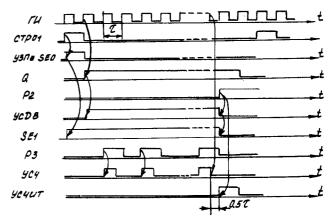

Схема алгоритма преобразования по выбранному варианту изображена на рис. 2.4. Составим соответствующее ей операционное описание синтезируемого устройства

(pac. 2.5).

В теле процедуры микропрограммы у переменных РГД и СЧЕ опущено поле разрядности. В этом случае его значение беретоя из раздела описания переменных микропрограммы. Под воздействием сигнала УСЧИТ не выполняется никакой операции. Этот факт отображается записью символа. ":" волед за оимволом ":", что равносильно введению пустой микрооперации.

Анализ микропрограммы показывает, что сигналы УЗАП и УН эквивалентны и их можно заменить одним сягналом УЗП: УЗП = УЗАП = УН. Проверку на ноль содержимого регистра РГЛ можно осуществить с помощью операции ИЛИ-НЕ (отрелка Пироа):

$$P2 = V P \Gamma \mathcal{L} \{i\} = V P \Gamma \mathcal{L} \{1:32\}.$$

Puc. 2.4

Текот микропрограммы, учитывающий вышесказанное, представлен на pag. 2.6.

#### 2.3.2. Разработка функциональной схемы устройства

Функциональная схема операционного автомата, составленная в соответствии с микропрограммой 2, изображена на рис. 2.7.

CTPOE:

A {I:32}

Переменные вжодние: внутрениие

виходние:

PI=CIPOE: P2-PUI

Признаки:

B{1:6}=CWE{1:6}

N

Микропрограмма ЧИСЛО ЕДИНИЦ;

Мижропрограмма ЧИСЛО ЕДИНИЦ;

Переменные

C理(I:6); CIPOE; B(I:6)=CUE (I:6) A{1:32} внутрениве: входние:

выходине:

PFI (I:32)=0;  $= P\Gamma\Pi\{I\}$

= CTPOE;

YSAII: Процедура

ecam 1PI,

P3+PII(I):

Процедура

벟

если

3

yaı:

ecam 图 PLI

H 翌

если 閔 PLI VCID: yc4: 9

ycqMT: M4

конец.

2 2 Pac.

**2**9 Pao.

идти к М2;

VCHB:

9

**y**C4:

ycqm:

M4

конеп.

PI Рис. 2.7

Задачи, решаемые управляющим автоматом, достаточно просты: он генерирует управляющие сигналы сдвига УСДВ до момента появления признака обнуления Р2, после чего формирует импульс считывания УСЧИТ. УА может быть построен как с жесткой логикой, так и с программируемой логикой. Рассмотрим оба способа реализации.

# Управляющий автомат с жесткой логикой

УА с жесткой логикой реализуется либо в виде классического конечного автомата, либо в виде распределителя импульсов. Конечный автомат может быть построен и как автомат Мура, и как автомат

Мили. Построение графов переходов и выходов УА осушествляется на основании отмеченных граф-схем алгоритмов [15]. На рис. 2.8 построены граф-схемы алгоритмов для автоматов Мура (а) и Мили (б), соответствующие микропрограмме 2 на рис.2.6 и учитывающие тот факт, что сигналы УСЧ и УСПВ являются совместными. Метки Q; отображаются в состояния автоматов, условия PI, P2, P3 определяют значения входных сигналов, а управляющие сигналы - значения выходных

a(t)4 QD Q(t)0 1 P2 P3 0 0 YCAB 0 0 YCH, YCAL (YE YUT 0 0 YC4U1 **У3**/7 YCHM **Y3**/7 (YCYUT) 0 *y3*17 YC4, YC48 0 УСД В

Таблица 3

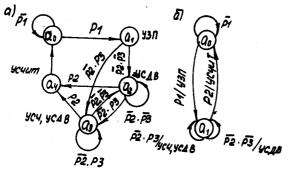

сигналов автоматов. Графы переходов для автоматов Мура и Мили. полученные из граф-схем алгоритмов, изображены на рис. 2.9,а и б.

Будем строить УА как автомат Мили, поскольку он имеет только два состояния и реализуется на одном триггере. В качестве по-

Рис. 2.9

следнего возьмем Д-триггер. На основании таблицы переходов и выходов УА (табл. 3) после доопределения запрещенных комбинаций получим функцию возбуждения триггера и выражения для управляющих сигналов:

$$D = P1 \cdot \overline{Q} + \overline{P2} \cdot Q,$$

$$Y3\Pi = P1 \cdot \overline{Q},$$

$$YC4 = YCB \cdot P3,$$

$$YC4\Pi = P2 \cdot Q,$$

$$YCB = \overline{P2} \cdot Q.$$

(2.1)

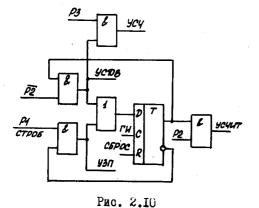

Функциональная схема УА приведена на рис. 2.10, сигнал СБРОС является установочным и формируется при включении питания или от кнопки.

#### Управляющий автомат с программируемой логикой

Составим каноническую форму микропрограммы синтезируемого операционного устройства с учетом эквивалентности сигналов УЗАП, УН и совместимости сигналов УСЧ, УСДВ в виде тасл. 4.

Таблица 4

| Номер | Метка | Управляющие сигналы | Переход          |

|-------|-------|---------------------|------------------|

| 0     | MI    |                     | Если 7 РІ, то МІ |

| I     |       | ASII                |                  |

| 2     | M2    | ·                   | Если Р2, то М4   |

| 3     |       |                     | Если 7 РЗ, то МЗ |

| 4     |       | усч, усдв           |                  |

| 5     |       |                     | Идти к М2        |

| 6     | МЗ    | УСДВ                | ·                |

| 7     |       | ·                   | Идти к М2        |

| 8     | M4    | усчит               |                  |

| 9     |       |                     | Конец            |

В случае принудительной адресации строки 4 и 5, 6 и 7, 8 и 9 можно объединить. Тогда каноническая форма операционного описания будет на три строки короче (табл. 5).

| Номер | Метка | Управляющие сигналы | Переход          |

|-------|-------|---------------------|------------------|

| 0     | MI    |                     | Если 7 РІ, то МІ |

| I     |       | <b>y</b> 3II        |                  |

| 2     | M2    |                     | Если Р2, то M4   |

| 3     |       |                     | Если 7 РЗ, то МЗ |

| 4     |       | усч, усдв           | Идти к М2        |

| 5     | МЗ    | УСЛВ                | Идти к М2        |

| 6     | M4    | усчит               | Конец            |

Формат команды с принудительной адресацией имеет вил [12]

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | усч | УСДВ | УСЧИТ | XPI | XP2 | XP3 | A2  | ΔΤ  | AO  |

|----------------------------------------|-----|------|-------|-----|-----|-----|-----|-----|-----|

|                                        |     |      |       |     |     |     | 220 | 7.1 | n.u |

Для естественной адресации имеется два формата микрокоманд [12]

| 0 | )3II | усч | ACTIB | усчит | _  | _  | _  |

|---|------|-----|-------|-------|----|----|----|

| I | XPI  | XP2 | XP3   | АЗ    | A2 | AI | OA |

Первий разряд формата микрокоманды УА с естественной адресацией определяет признак микрокоманды: 0 — операционная микрокоманда. I — управляющая микрокоманда.

Учитывая, что табл. 4 дает каноническое описание микропрограммы для УА с естественной адресацией, получаем кодовые выражения микропрограмм для УА с естественной адресацией (табл. 6) и с принудительной адресацией (табл. 7):

Таблица 6

Таблица 7

| Адрес | Pa | аряды микрокоманд |

|-------|----|-------------------|

| 0000  | I  | I00 0000          |

| 0001  | 0  | I 0 0 0 0 0 0     |

| 0010  | I  | 010 1000          |

| IIGO  | I  | 001 0110          |

| 0100  | 0  | 0000 110          |

| 0101  | Ι  | 000 0010          |

| 0110  | 0  | 0000 100          |

| OIII  | I  | 000 0100          |

| 1000  | 0  | 000 1000          |

| I000  | I  | 000 0000          |

| Адрес | Разряды микрокоманд |

|-------|---------------------|

| 000   | 0000 100 000        |

| 100   | 1000 000 010        |

| 010   | 0000 010 110        |

| OII   | 0000 001 101        |

| 100   | 0110 000 010        |

| IOI   | 0010 000 010        |

| IIO   | 0001 000 000        |

Из сравнения табл. 6 и 7 следует, что для хранения микропрограммы с естественной адресацией требуется 80 бит, а для УА с при-

нудительной адресацией — 70 бит. Таким образом, реализация УА с принудительной адресацией в нашем случае более желательна.

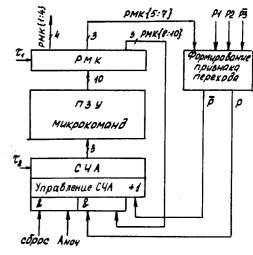

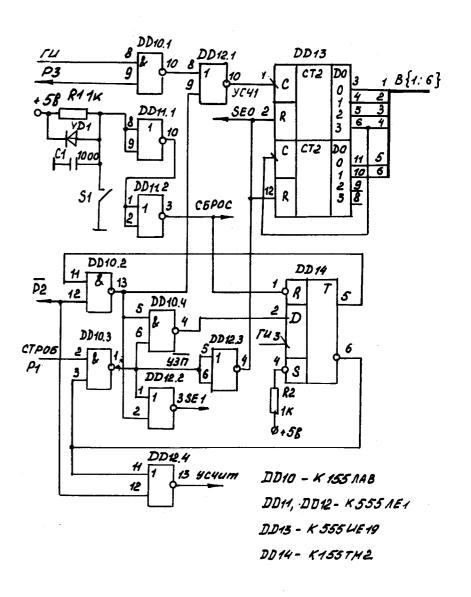

на рис. 2.II изображена функциональная схема УА с принудительной адресацией. Управляющие сигнали формируются регистром микрокоманды (РМК), в который микрокоманда переписывается из ПЗУ микрокоманд по адресу, находящемуся в счетчике адреса (СЧА). Регистр РМК тактируется последовательностью 7, а счетчик адреса СЧА — последовательностью 7, 2 с 7, 2 7, 2 0.

Рис. 2.II

Начальный адрес микропрограмми, равный 000, устанавливается сигналом СБРОС, и УА ждет прихода сигнала СТРОБ для продолжения работы.

Не будем приводить принципиальную схему УА, поскольку она является стандартной. Пусть переход от функциональной схемы УА к принципиальной, выполненной на заданной элементной базе, станет составной частью проекта.

При построении принципиальной схемы выберем УА с жесткой логикой, поскольку он имеет более простую организацию, чем УА с программируемой логикой.

# 2.3.3. Построение принципиальной схемы

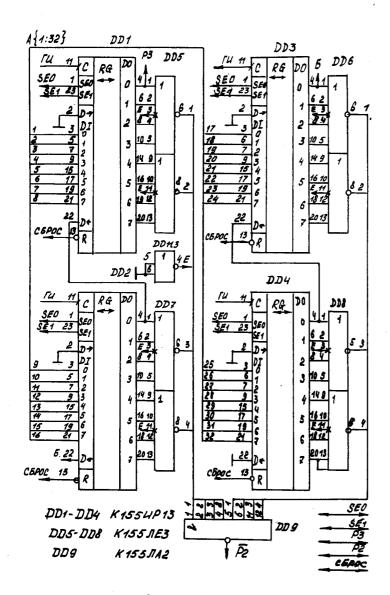

Будем строить наше устройство на элементах серии КІ55 и К555, так как они обеспечивают устойчивую работу на заданной тактовой частоте 5 МГц. Принципиальные схемы устройства, построенные по функциональным схемам рис. 2.7 и 2.10, изображены на рис. 2.12 и 2.13. Регистр данных РГД строится на четырех микросхемах 8-разрядных сдвигающих регистров КІ55ИРІЗ. Управляющие сигналы SEO, SEI обеспечивают запись кода A в регистр (SEO=1, SEI=1) и сдвиг влево (SEO=0, SEI=1). Они формируются из управляющих сигналов УА в соответствии с уравнениями

Puc. 2.12

Puc. 2.13

Здесь с учетом логических выражений (2.1) и выбранной элементной базы

$$\frac{\overline{y_3}\overline{\eta} = PI/\overline{Q}}{y_{\zeta}QB} = \overline{P2}/Q. \tag{2.2}$$

Сигнал возбуждения Д-триггера на микросхеме DD14 типа К155TM2, и опользуемого для построения УА, на основании (2.1) и (2.2) запишется следующим образом:

$$D = (PI/QI)/(PZ/Q) = \overline{Y3\Pi}/\overline{YCAB}. \qquad (2.3)$$

Счетчик собирается на микросхеме К555ИЕІЭ, включающей два 4-разрядных асинхронных счетчика с последовательным переносом. Для его работы сигнал УСЧ необходимо стробировать тактовыми импульсами IV:

$$\mathcal{Y}C\mathcal{U}\mathcal{I} = \mathcal{Y}C\mathcal{U} \cdot \mathcal{T} = (\mathcal{Y}C\mathcal{L}B \cdot P\mathcal{I})\mathcal{T} = \overline{\mathcal{Y}C\mathcal{L}B} \downarrow (P\mathcal{I}/\mathcal{T}).$$

Сигнал УСЧИТ в соответствии с (2.1) формируется на элементе DD12.4, выполняющем функцию ИЛИ-НЕ (стрелку Пирса):

При его формировании необходимо организовать такой временной интервал между последним импульсом УСЧІ и УСЧИТ, чтобы гарантировать завершение всех переходных процессов в последовательном счетчике на К555ИЕІ9 (60 нс на четыре разряда, 90 нс на шесть разрядов). Работа устройства демонотрируется эпюрами напряжений на рис. 2.14. Суммарная задержка фронта импульса УСЧИТ относительно среза импульса УСЧІ — не менее 100 нс. Таким образом, к началу импульса УСЧИТ все переходные процессы в счетчике DDІЗ завершатся, и выходной код В  $\{1:6\}$  установится.

Устройство требует для своего построения 14 корпусов микросхем, среди них: по четыре микросхемы К155ИРІЗ и К155ЛЕЗ, по одной микросхеме К155ЛАЗ, К155ТМЗ, К555ИЕІ9, К155ЛАЗ и две микросхемы К555ЛЕІ.

Puc. 2.14

Разработанная схема обеспечивает время преобразования от 0,25 мкс (нулевой код) до 6,25 мкс (код всех единиц) при потребляемой от источника +5 В мощности 3,5 Вт.

# 2.4. ПОСТРОЕНИЕ УСТРОЙСТВА В ВИДЕ МИКРОПРОЦЕССОРНОГО ВЫЧИСЛИТЕЛЯ НА БИС КР580ВМ80

Микропроцессорный вычислитель имеет стандартную структуру. Поэтому его схему строить не надо. Единственной задачей остается создание программируемого контроллера интерфейса, обеспечивающего подключение к вычислителю источника и потребителя информации, управляющей программы обмена контроллера, называемой драйвером, и обрабатывающей программы.

В отличие от рассмотренных ранее вариантов построения преобразователя в виде самостоятельного устройства для микропроцессорного варианта подсчет числа единиц кода осуществляется с помощью обрабатывающей программы. Поэтому ее написание и отладка является важным этапом в построении устройства, включающем следующие шаги:

- I) разработку обрабатывающего алгоритма;

- 2) составление программы на языке ассемолера;

- 3) отладку и выполнение программы.

Третий шаг требует дополнительных пояснений. Отладку и выполнение программы можно осуществить либо на микроЭВМ и персональных ЭВМ, имеющих транслятор с языка ассемблера КР58ОВМ8О или языков ассемблеров, включающих его как подмножество, либо на лабораторной

микроЭВМ "Микролаб". В последнем случае необходимо выполнить ручное ассемблирование программы.

При составлении алгоритма необходимо учитывать, что микропроцессорный вычислитель имеет байтовую организацию памяти и 8-разрядную шину данных. Обобщим исходную задачу, положив, что входной код, число единиц которого подсчитывается после размещения его в памяти, занимает массив из 77 байтов.

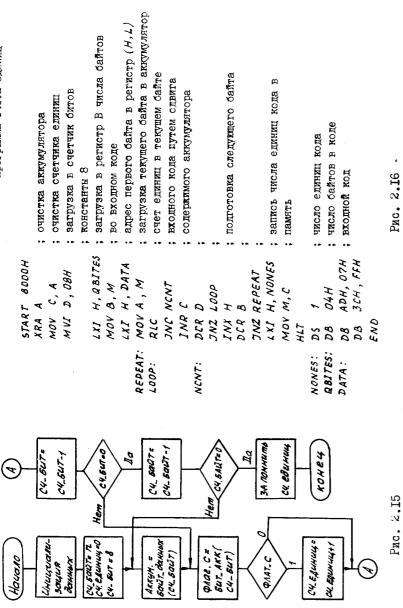

Схема алгоритма изображена на рис. 2.15. Алгоритм включает в себя два цикла: подсчет числа единиц в текущем байте и накопление единиц при просмотре всех байтов. Входной код размещается в массиве БАЙТ\_ДАННЫХ. Положение текущего байта в массиве определяется счетчиком байтов СЧ\_БАЙТ. Положение текущего бита этого байта, предварительно помещенного в аккумулятор, определяется СЧ\_БИТ.

Программа, реализованная по данному алгоритму, представлена на рис. 2.16. Просмотр битов текущего байта осуществляется путем сдвига аккумулятора, при этом анализируемый бит кода формирует значение признака переноса С. Окончание просмотра осуществляется по нулевому содержимому счетчика битов, расположенного в регистре В. Просмотр байтов кода завершается, когда обнуляется счетчик байтов, расположенный в регистре С. Программа загружается в ОЗУ по адресу 8000.

Для успешного выполнения курсовой работы необходимо, чтобы студент умел пользоваться и ориентироваться в научной и справочной литературе по тематике курсовой работы. Чтобы помочь студенту в этом, ниже приводится указатель литературы, сгруппированной по отдельным разделам работы.

#### PEKOMEHIIYEMAR JINTEPATYPA

#### Общие вопросы

- І. Каган Б.М. Электронные вычислительные машины и си- стемы. М.: Энергоатомиздат, 1985.

- 2. У окерли Дж. Архитектура и программирование микро-ЭВМ: В 2-х кн. - М.: Мир, 1984.

- 3. Бруснецов Н.П. Микрокомпьютеры. М.: Наука, 1985.

- 4.  $\Gamma$  и л м о р Ч. Введение в микропроцессорную технику. М.: Мир, 1984.

- 5. Микропроцессоры: В 3-х кн. / Под ред. Л.Н. Преснухина. М.: Высшая школа. 1986.

- 6. Кондратьев Р.М., Мельников Б.С., Щеглов А.В. Архитектура микропроцессорных вычислителей. — М.: МАИ, 1986.

# <u>Языки операционного описания, языки регистровых передач</u> <u>и синтез операционных устройств</u>

- 7. Автоматизация проектирования вычислительных систем, языки моделирования и базы данных / Под ред. М. Брейера. М.: Мир.1979...

- 8. Проектирование цифровых вычислительных машин / Под ред. С.А. Майорова. - М.: Высшая школа, 1972.

- 9. Майоров С.А., Новиков Г.И. Принципы организации цифровых машин. Л.: Машиностроение, 1974.

- 10. Ч у Я. Организация ЭВМ и микропрограммирование. М.: Мир, 1975.

- II. Силин В.Б., Мельников Б.С. Электронные вычислительные устройства. Операционный синтез. - М.: МАИ, 1982.

- I2. Силин В.Б., Мельников Б.С., Кондратье в Р.М. Операционный синтез цифровых устройств. М.: МАИ. 1985.

#### Построение управляющих автоматов

- I3. Силин В.Б., Мельников Б.С. Конечные автомати: Учебное пособие. М.: МАИ. 1978.

- I4. Лазарев В.Г., Пийль Е.И. Синтез управляющих автоматов. М.: Энергия, 1978.

- I5. Баранов С.И. Синтез микропрограммных автоматов. И.: Энергия, 1978.

- I6. Специализированные ЦВМ / Под ред. В.Б. Смолова. М.: Высшая школа, 1981.

#### Программирование микропроцессорных вычислителей

- 17. Григорьев В.Л. Программное обеспечение микропроцессорных систем. - М.: Энергоатомиздат, 1983.

- 18. Григорьев В.Л. Программирование однокристальных микропроцессоров. М.: Энергоатомиздат, 1987.

#### Организация и технические средства микропроцессорных систем

- ІЭ. Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы. - М.: Радио и связь, 1989.

- 20. К о ф ф р о н Дж. Технические средства микропроцессорных систем: Практический курс. М.: Энергоатомиздат, 1983.

- 2І. Коффрон Дж., Ленг В. Расширение микропроцессорных систем. М.: Машиностроение, 1987.

- 22. Микропроцессорный комплект КІВІО: Структура, программирование, применение: Справочная книга / Под ред. Ю.М. Казаринова. М.: Радио и связь, 1990.

- 23. Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения. М.: Радио и связь, 1986.

#### Схемстехника электронных схем

- 24. Титце У., Шенк К. Полупроводниковая схемотехни-ка. М.: Мир, 1982.

- 25. Хоровиц П., Хилл У. Искусство схемотехники: В 2-х т. - М.: Мир, 1983.

#### Справочная литература

26. Интегральные микросхемы: Справочник / Под ред. В.В. Тарабрина. - М.: Радио и связь, 1984.

- 27. Хвощ С.Т., Варлинский Н.Н., Попов Е.А. Микропроцессоры и микроЭВМ в системах автоматического управления: Справочник. Л.: Машиностроение, 1987.

- 28. Шило В.Л. Популярные цифровые микросхемы: Справочник. М.: Радио и связь. 1987.

- 29. Цифровые и аналоговые интегральные микроохемы: Справочник / Под ред. С.В. Якубовского. М.: Радио и связь, 1990.

- 30. Применение интегральных микросхем в электронной вычислительной технике: Справочник / Под ред. Б.Н. Файзулаева, Б.В. Тарабрина. - М.: Радио и связь, 1987.

- ЗІ. П ухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. М.: Радио и связь, 1990.

- 32. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник / Под ред. В.А. Шахнова. М.: Радио и связь. 1988.

- 33. Лебедев О.Н. Микроохемы памяти и их применение. М.: Радио и связь, 1990.

- 34. Полупроводниковые БИС запоминающих устройств: Справочник / Под ред. А.Ю. Гордонова и Ю.Н. Дьякова. М.: Радио и связь, 1990.

- 35. Большие интегральные схемы запоминающих устройств: Справочник / Под ред. А.Ю. Гордонова и Ю.Н. Дьякова. М.: Радио и связь, 1990.

- 36. Система документации единой системы ЭВМ / Под общ. ред. А.М. Ларионова. М.: Статистика, 1976.

- 37. У сатенко С.Т., Каченюк Т.К., Терехова М.В. Выполнение электрических схем по ЕСКД: Справочник. — М.: Изд-во стандартов. 1989.

#### OTJIABJIEHME

| I. Требования к выполнению и оформлению курсовой  |    |

|---------------------------------------------------|----|

| аботы                                             | 3  |

| I.I. Цель и задачи куроовой работы                | 3  |

| I.2. Задание на курсовую работу                   | 3  |

| 1.3. Порядок выполнения курсовой работы           |    |

| I.4. Оформление курсовой работы                   | 8  |

| I.5. Календарный план выполнения курсовой работы  |    |

| 2. Пример построения цифрового устройства         | IJ |

| 2.І. Задание на проектирование                    | IJ |

| 2.2. Комбинационная реализация устройства         |    |

| 2.3. Регистровая реализация устройства            |    |

| 2.4. Построение устройства в виде микропроцессор- |    |

| ого вычислителя на БИС КР580ВМ80                  | 27 |

| Рекомендуемая литература                          |    |

| - # #                                             |    |